6.2 KONFIGURASI BIAS TETAP

- untuk memahami materi konfigurasi bias tetap

- untuk mengetahui perhitungan pada konfigurasi bias tetap

2. Alat dan bahan[kembali]

- Baterai, berfungsi sebagai sumber arus listrik.

- LED Green, berfungsi sebagai indikator atau sinyal indikator/lampu indikator.

- Resistor, berfungsi sebagai pembagi, pembatas, dan pengatur arus dalam suatu rangkaian.Resistor 1k OhmResistor berfungsi untuk menghambat arus dalam rangkaian listrik. Cara menghitung nilai resistansi resistor dengan gelang warna :1. Masukan angka langsung dari kode warna gelang pertama.2. Masukan angka langsung dari kode warna gelang kedua.3. Masukan angka langsung dari kode warna gelang ketiga.4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n), ini merupakan nilai toleransi dari resistor.

- Ground, berfungsi sebagai penghantar arus listrik langsung ke bumi.

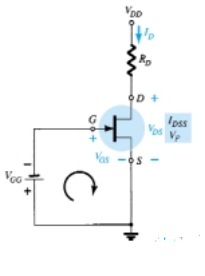

Pengaturan

bias yang paling sederhana untuk JFET n-channel

muncul pada Gambar dibawah Disebut sebagai konfigurasi bias tetap, ini adalah

salah satu dari sedikit konfigurasi FET yang dapat diselesaikan secara langsung

dengan menggunakan pendekatan matematika atau grafis. Kedua metode dimasukkan

dalam bagian ini untuk menunjukkan perbedaan antara keduanya dan juga untuk

menetapkan fakta bahwa solusi yang sama dapat diperoleh dengan menggunakan

metode mana pun.

Konfigurasi

Gambar diatas mencakup level ac Vi

dan Vo dan

kopling kapasitor (C1

dan C2). Ingatlah

bahwa kapasitor kopling adalah "sirkuit terbuka" untuk analisis dc

dan impedansi rendah (pada dasarnya hubung singkat) untuk analisis ac. Itu

resistor RG hadir untuk

memastikan bahwa Vi muncul

pada input ke penguat FET untuk analisis ac (Bab 9). Untuk analisis dc,

Penurunan

nol-volt di RG memungkinkan

penggantian RG dengan arus

hubung singkat, seperti muncul di jaringan pada Gambar dibawah khusus digambar

ulang untuk analisis dc.

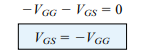

Fakta bahwa terminal negatif baterai terhubung langsung ke potensial positif yang ditentukan dari VGS dengan jelas menunjukkan bahwa polaritas VGS secara langsung berlawanan dengan VGG. Menerapkan hukum tegangan Kirchhoff searah jarum jam loop yang ditunjukkan pada Gambar diatas akan menghasilkan

Karena VGG adalah suplai dc tetap, tegangan VGS ditetapkan besarnya, menghasilkan notasi "konfigurasi bias tetap".

Tingkat yang dihasilkan dari ID arus drain sekarang dikontrol oleh persamaan Shockley :

Karena VGS adalah besaran

tetap untuk konfigurasi ini, besar dan tandanya hanya bisa diganti ke persamaan

Shockley dan tingkat ID yang

dihasilkan dihitung. Ini adalah salah satu dari sedikit contoh di mana solusi

matematika untuk konfigurasi FET.

Analisis

grafis akan membutuhkan plot persamaan Shockley seperti yang ditunjukkan pada

grafik dibawah(grafik 1). Ingatlah, bahwa memilih VGS = VP

/2 akan menghasilkan arus drain IDSS/4

saat membuat persamaan.

Pada Grafik 2, level tetap VGS telah dilapiskan sebagai garis vertikal di VGS VGG. Di titik mana pun pada garis vertikal, level VGS adalah VGG = - level ID harus ditentukan pada garis vertikal ini.

(Grafik 2)

Intersect

adalah solusi umum untuk konfigurasi yang biasanya disebut sebagai titik

operasi. Subskrip Q akan diterapkan untuk mengalirkan arus dan tegangan ke sumber

untuk mengidentifikasi levelnya pada titik Q. Perhatikan pada (grafik 2) bahwa level

diam ID ditentukan dengan menggambar garis horizontal dari titik Q ke sumbu ID

vertikal seperti yang ditunjukkan pada (grafik 2). level DC dari ID

dan VGS akan diukur

dengan meter seperti Gambar

dibawah adalah nilai diam/0 yang

ditentukan oleh grafik

2.

Tegangan drain-to-source dari bagian keluaran dapat ditentukan dengan menerapkan Hukum tegangan Kirchhoff sebagai berikut:

Ingatlah bahwa tegangan subskrip tunggal mengacu pada

tegangan pada suatu titik sehubungan dengan tanah. Untuk konfigurasi rangkaian

dibawah

Gunakan

notasi subskrip ganda :

EXAMPLE :

1.Tentukan nilai-nilai berikut pada rangkaian dibawah

a) VGSQ

b) IDQ

c) VDS

d) VD

e) VG

f) VS

Solusi :

PROBLEM

Solusi :

2. Tentukan VD untuk konfigurasi bias tetap pada Gambar!

Solusi :

4. PILIHAN GANDA[kembali]

1. Tentukan nilai tegangan VDSQ pada gambar rangkaian dibawah !

b. 7,94

c. 6,36

d. 5,87

Solusi :

2. Tentukan VD untuk konfigurasi bias tetap pada dibawah!

b. 18V

Solusi :

5. Percobaan[kembali]

a. Gambar Rangkaian

Tidak ada komentar:

Posting Komentar