7.3 Arithmetic Circuits – Basic Building Blocks

- untuk memahami materi arimatika sirkuit

- untuk menyelesaikan permasalahan terkait materi aritmatika sirkuit

1. Gerbang AND (AND Gate)

Gerbang AND termasuk yang paling sederhana diantara lainnya, dimana gerbang ini membutuhkan dua input untuk menghasilkan satu output. Sistemnya terdiri dari 0 dan 0 akan menghasilkan 0, 1 dan 0 akan menghasilkan 0, 1 dan 1 akan menghasilkan 1.

2. Gerbang OR (OR Gate)

Selanjutnya terdapat Gerbang OR atau OR Gate, gerbang ini sebenarnya hanya berbeda sedikit dari AND. Karena ia memiliki konfigurasi input 0 dan 0 akan menghasilkan 0, 0 dan 1 akan menghasilkan 1, 1 dan 0 akan menghasilkan 1, lalu 1 dan 1 akan menghasilkan 1.

Gerbang ini biasa digunakan untuk melengkapi sebuah sistem digital, dimana ia berfungsi agar sistem digital memiliki opsi yang lebih luas terhadap sistem geraknya

3. Gerbang NOT (NOT Gate) atau Inverter

Disebut juga sebagai Inverter (pembalik), Gerbang NOT memang memiliki konfigurasi terbalik. Ia dapat mengubah input 0 menjadi output 1, sedangkan input 0 akan menjadi output 1. Gerbang NOT juga sangat berbeda dengan gerbang lainnya, karena ia hanya mempunyai 1 input dan 1 output saja.

Umumnya Gerbang NOT di simbolkan dengan lambang (-) diatas variabel lainnya, hal tersebut bertujuan agar penggunaannya tidak salah atau keliru. Hal ini karena ia berguna sebagai pembalik dan berfungsi sangat vital dalam sistem digital.

4. Gerbang X-OR (X-OR Gate)

Ada juga versi Gerbang X-OR atau bisa disebut Exclusive OR, seperti namanya ia adalah versi pengembangan dari Gerbang OR. Konfigurasinya sendiri terdiri dari input 0 dan 0 menjadi 0, 0 dan 1 menjadi output 1, 1 dan 0 menjadi 1, lalu 1 dan 1 menjadi 0.

5. Logic Probe

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan

mengecek status logika (High atau Low) yang keluar dari rangkaian digital. Objek yang diukur

oleh logic probe ini adalah tegangan oleh karena itu biasanya rangkaian logic probe harus

menggunakan tegangan luar (bukan dari rangkaian logika yang ingin diukur) seperti baterai. Alat

ini biasa digunakan pada IC TTL ataupun CMOS (Complementary metal-oxide semiconductor).

Pada bagian ini, kita akan membahas blok bangunan logika kombinasional yang dapat digunakan untuk melakukan operasi penjumlahan dan pengurangan bilangan biner. Penjumlahan dan pengurangan adalah dua yang paling operasi aritmatika yang umum digunakan, karena dua lainnya, yaitu perkalian dan pembagian, adalah masing-masing proses penambahan berulang dan pengurangan berulang. Blok bangunan dasar yang membentuk dasar dari semua perangkat keras yang digunakan untuk melakukan operasi aritmatika tersebut adalah half-adder, full adder, half-subtractor, full subtractor, dan control inverter.

1. Half-Adder

Half-Adder adalah blok rangkaian aritmatika yang dapat digunakan untuk menjumlahkan dua bit. Sirkuit seperti itu memiliki dua input yang mewakili dua bit yang akan ditambahkan dan dua output, dengan satu menghasilkan output SUM dan yang lainnya memproduksi CARRY.

Ekspresi Boolean untuk output SUM dan CARRY diberikan oleh persamaan

Gambar 1 Tabel kebenaran setengah penambah.

Gambar 2 Implementasi logika half-adder.

2. Full Adder

Sirkuit Full Adder adalah blok sirkuit aritmatika yang dapat digunakan untuk menambahkan tiga bit untuk menghasilkan SUM dan keluaran CARRY.

Gambar 3 Implementasi half-adder menggunakan gerbang NAND.

Gambar 4 Tabel kebenaran full adder.

Gambar 4 menunjukkan tabel kebenaran dari rangkaian penambah penuh yang menunjukkan semua kemungkinan kombinasi input dan output yang sesuai. Untuk sampai pada rangkaian logika untuk implementasi perangkat keras secara penuh penambah, pertama-tama kita akan menulis ekspresi Boolean untuk dua variabel keluaran, yaitu, SUM dan CARRY output, dalam hal variabel input. Ekspresi Boolean untuk dua variabel output diberikan dalam Persamaan (7.7) untuk SUM output (S) dan dalam Persamaan (6.6) untuk

CARRY keluaran (Cout):

Peta Karnaugh untuk dua ekspresi diberikan pada Gambar 5(a) untuk keluaran SUM dan Gambar 5(b) untuk keluaran CARRY. Seperti yang jelas dari dua peta, ekspresi untuk SUM (S output tidak dapat disederhanakan lagi, sedangkan ekspresi Boolean yang disederhanakan untuk Cout diberikan

dengan persamaan

Gambar 6 menunjukkan diagram rangkaian logika dari penambah penuh. Sebuah penambah penuh juga dapat dilihat terdiri dari dua setengah penambah dan gerbang OR. Ekspresi untuk output SUM dan CARRY dapat ditulis ulang sebagai :

Gambar 5 Peta Karnaugh untuk penjumlahan dan pelaksanaan sebuah penjumlah penuh.

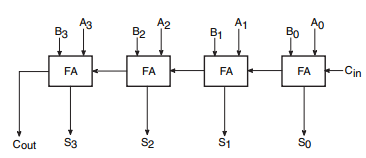

Penjumlah penuh dari tipe yang dijelaskan di atas membentuk blok bangunan dasar dari penambah biner. Namun, sirkuit penambah penuh tunggal dapat digunakan untuk menambahkan angka biner satu bit saja

Gambar 6 Diagram rangkaian logika penambah penuh.

3. Half Subtractor

Half-Subtractor adalah rangkaian kombinasional yang dapat digunakan untuk mengurangi satu digit biner dari yang lain untuk menghasilkan keluaran PERBEDAAN dan keluaran PINJAMAN. Output BORROW di sini menentukan apakah '1' telah dipinjam untuk melakukan pengurangan. Tabel kebenaran setengah-pengurang, sebagai ditunjukkan pada Gambar 9 , menjelaskan hal ini lebih lanjut. Ekspresi Boolean untuk dua output diberikan oleh persamaan.

Gambar 7 Implementasi logika full adder dengan half-adder.

Gambar 8 Penjumlah biner empat bit.

Jelas bahwa tidak ada ruang lingkup lebih lanjut untuk penyederhanaan ekspresi Boolean yang diberikan dengan Persamaan 9 dan 10.

Gambar 9 Half-Subtractor

Gambar 10 Diagram logika Half-Subtractor

Gerbang X-OR, ekspresi untuk output BORROW (Bo) adalah gerbang AND dengan input A dilengkapi sebelum diumpankan ke gerbang. Gambar 7.13 menunjukkan implementasi logika a setengah-pengurang. Membandingkan setengah-pengurang dengan setengah-penambah, kami menemukan bahwa ekspresi untuk Output SUM dan DIFFERENCE sama saja. Ekspresi untuk BORROW dalam kasus setengah-pengurang juga mirip dengan apa yang kita miliki untuk CARRY dalam kasus setengah-penambahan. Jika input A, yaitu minuend, dilengkapi, gerbang AND dapat digunakan untuk mengimplementasikan keluaran PINJAMAN. Perhatikan persamaan antara diagram logika Gambar 2 (setengah penambah) dan Gambar 10 (setengah-pengurang).

4. Full Subtractor

Pengurang penuh melakukan operasi pengurangan pada dua bit, minuend dan subtrahend, dan juga mengambil mempertimbangkan apakah '1' telah dipinjam oleh bit minuend bawah yang berdekatan sebelumnya atau tidak. Akibatnya, ada tiga bit yang harus ditangani pada input pengurang penuh, yaitu dua bit untuk dikurangkan dan bit pinjaman ditunjuk sebagai Bin. Ada dua output, yaitu PERBEDAAN

keluaran D dan keluaran BORROW Bo.

Ekspresi Boolean untuk dua variabel output diberikan oleh persamaan

Gambar 11 Tabel kebenaran sebuah pengurang penuh.

Gambar 12 Peta Karnaugh untuk output perbedaan dan pinjaman.

Peta Karnaugh untuk dua ekspresi diberikan pada Gambar 12(a) untuk keluaran DIFFERENCE D dan pada Gambar 12(b) untuk keluaran BORROW Bo. Seperti yang jelas dari dua peta Karnaugh, tidak ada penyederhanaan dimungkinkan untuk keluaran perbedaan D. Ekspresi yang disederhanakan untuk Bo diberikan oleh persamaan

Gambar 13 Implementasi logika dari full subtractor dengan half-subtractor.

5. Controlled Inverter

Inverter terkontrol diperlukan ketika penambah akan digunakan sebagai pengurang. Seperti yang diuraikan sebelumnya, pengurangan tidak lain adalah penambahan komplemen 2 dari pengurangan ke minuend. Dengan demikian, Langkah pertama menuju implementasi praktis dari sebuah subtractor adalah menentukan komplemen 2 dari pengurang. Dan untuk ini, pertama-tama kita perlu menemukan pelengkap 1

Gambar 14 Pengurang empat bit

Sebagai contoh, 11010010 pada input akan menghasilkan 00101101 pada output ketika input kontrol dalam keadaan logika '1'.

1) Lihat Gambar 7.26. Tulis ekspresi Boolean yang disederhanakan untuk keluaran DIFFERENCE dan BORROW

Solusi :

Mari kita asumsikan bahwa dua input ke rangkaian setengah-pengurang adalah X dan Y , dengan X sama dengan SUM output dari setengah penambah dan Y sama dengan C. output DIFFERENCE dan BORROW kemudian dapat diungkapkan sebagai berikut:

Juga, Substitusikan nilai X dan Y , diperoleh

2) Mengingat ekspresi Boolean yang relevan untuk rangkaian setengah-penambah dan setengah-pengurang, rancang rangkaian setengah-penambah-pengurang yang dapat digunakan untuk melakukan penjumlahan atau pengurangan pada dua bit satu angka. Operasi aritmatika yang diinginkan harus dapat dipilih dari input kontrol.

Solusi

Ekspresi Boolean untuk setengah-penambah dan setengah-pengurang diberikan sebagai berikut:

Half-adder

Half-subtractor

DIFFERENCE output = AB +AB and BORROW output= AB

Jika kita menggunakan inverter terkontrol untuk melengkapi A dalam kasus rangkaian setengah-pengurang, maka perangkat keras yang sama juga dapat digunakan untuk menambahkan dua angka satu bit. Gambar 7.25 menunjukkan rangkaian logika

diagram. Ketika input kontrol adalah '0', variabel input A dilewatkan tanpa pelengkap ke input dari gerbang NAND. Dalam hal ini, gerbang AND menghasilkan keluaran CARRY dari operasi penjumlahan. Itu Gerbang EX-OR menghasilkan keluaran SUM. Di sisi lain, ketika input kontrol adalah '1', AND gerbang menghasilkan keluaran BORROW dan gerbang EX-OR menghasilkan keluaran PERBEDAAN. Dengan demikian, '0' pada input kontrol menjadikannya setengah penambah, sedangkan '1' pada input kontrol menjadikannya setengah-pengurang.

B) Problem

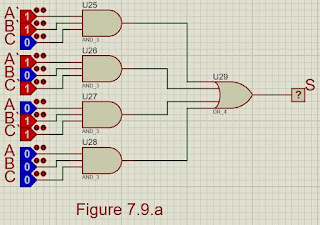

1. Jika input A diberi logik 0 dan inout B diberi logik 1 maka apa yang akan terjadi?

Solusi :

Maka pada logic probe S akan berlogika 1 dan logic probe C akan berlogika 0

2. Jika logic state input ABC diberi logika 010 maka apa yang akan terjadi pada logic probe?

Solusi :

Yang terjadi pada logic probe DC akan berlogika 10

8. Dekorder adalah …

a. Rangkaian yang mempunyai nilai keluaran di suatu waktu hanya ditentukan oleh nilai dari masuknya di waktu tersebut

b. Rangkaian yang digunakan untuk memperbanyak jumlah output

c. Alat yang digunakan untuk mengembalikan proses encoding sehingga dapat melihat atau menerima informasi aslinya *

d. Rangkaian yang berupa flip-flop yang bisa menyimpan sebuah data

e. Komponen yang bekerja dengan menyimpan muatan

9. Fungsi dekorder adalah …

a. Menghasilkan bentuk gelombang yang ada

b. Memudahkan dalam menyalakan seven segment *

c. Dapat memproses data biner secara bersamaan

d. Dapat menentukan perjalanan data dari satu sumber

e. Sebagai alat selector

a. Gambar Rangkaian

b. Vidio Rangkaian

.png)

.png)

.JPG)

Tidak ada komentar:

Posting Komentar