LAPORAN AKHIR 1

PERCOBAAN 1

M3

2. Alat dan Bahan [kembali]

|

Gambar 1 Module D`Lourenzo

| | Gambar 2 Jumper |

|

2.2. Software (Bahan Proteus)

a. Gerbang XOR (IC 7486)

|

| Gambar 3 |

b. Gerbang OR (IC 7432)

|

| Gambar 4 |

c. Gerbang AND (IC 7408)

|

| Gambar 5 |

d. Gerbang XNOR (IC 4077)

|

| Gambar 6 |

e. Gerbang NOR (IC 7402)

|

| Gambar 7 |

f. Gerbang NAND (IC 7400)

|

| Gambar 8 |

g. Switch (SW-SPDT)

|

| Gambar 9 |

h. Power DC

|

| Gambar 10 |

i. LogicProbe atau LED

|

| Gambar 11 |

j. Resistor

|

| Gambar 12 |

k. Ground

|

| Gambar 13 |

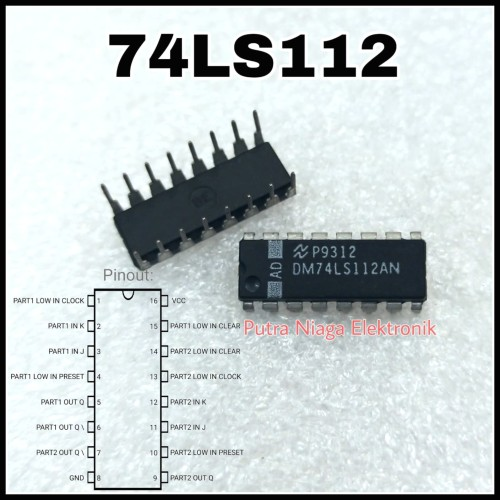

l. IC 74LS112

m. IC 74LS90

n. IC 7493

o. IC 74193

p. IC 74192

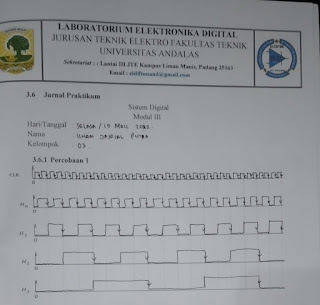

Berdasarkan IC yang digunakan Pada Percobaan 1 Yaitu. IC 74LS112, Yaitu dimana hasil output yang diberikan dari IC tersebut yang dirancang Sebagai rangkaian JK Flip-Flop, berupa Counter UP Pada counter Asyncronus tersebut karena pada perubahan bilangan biner dimulai dari 0000 hingga 1111 atau jumlah bitnya 0 hingga 15.

2] Analisa sinyal output yang dikeluarkan jk flipflop kedua dan ketiga?

Pada sinyal output JK flip-flop kedua dimana inputnya berasal dari Output JK fliP-flop Pertama Dimana Pada JK flip-flop Pertama membutuhkan 2 kali Clock untuk Merubah Outputnya dan karena input JK flip-flop Pertama adalah input JK flip-flop kedua maka akan berloglika 1 atau high, ketika H0 berlogika 'O' atau low dan Pada JK flip-flop kedua akan membutuhkan 4 kali clock untuk mengubah outputnya.

Pada sinyal output JK Flip-Flop ketiga dimana input dari Jk flip- flup ketiga adolah output dan JK flip-flop kedua Sehingga H2 akan berlogika 1 apabila H1 Clock Pertama berlogika 0 dan Jk flip-flop ketiga membutuhkan 8 Clock untuk mengubah inputnya.

File Rangkaian Percobaan Link Datasheet JK Flipflop Link Datasheet D Flipflop Link

Datasheet T Flipflop Link Datasheet IC 74LS160 Link

Datasheet IC 74LS161 Link

Tidak ada komentar:

Posting Komentar