LAPORAN AKHIR 2

PERCOBAAN 3

M4

2.1 Hardware

| ||

Gambar 1 Module D`Lourenzo

|

a. Gerbang XOR (IC 7486)

|

| Gambar 3 |

b. Gerbang OR (IC 7432)

|

| Gambar 4 |

c. Gerbang AND (IC 7408)

|

| Gambar 5 |

d. Gerbang XNOR (IC 4077)

|

| Gambar 6 |

e. Gerbang NOR (IC 7402)

|

| Gambar 7 |

f. Gerbang NAND (IC 7400)

|

| Gambar 8 |

g. Switch (SW-SPDT)

|

| Gambar 9 |

h. Power DC

|

| Gambar 10 |

i. LogicProbe atau LED

|

| Gambar 11 |

j. Resistor

|

| Gambar 12 |

k. Ground

|

| Gambar 13 |

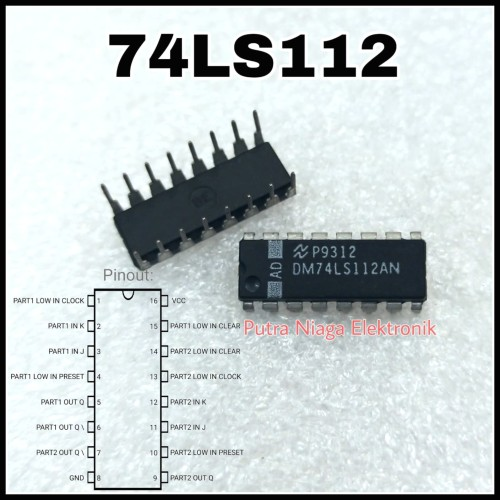

l. IC 74LS112

m. IC 74LS90

n. IC 7493

o. IC 74193

p. IC 74192

q. IC 74LS47

r. Seven Segment

1] Analisa output yang dihasilkan tiap tiap kondisi !

Pada kondisi 1, dimana diberi kondisi pada switch B0 menjadi "0", B2 menjadi "0" serta B3 menjadi clock. maka, output yang diberikan yaitu dimana seven segment tidak dapat menyala.

Pada kondisi 2, dimana diberi kondisi switch B0 menjadi 0, B2 menjadi 1 serta B3 diberi clock . maka, output yang diberikan atau yang terjadi yaitu seven segment hidup dan hitung mundur dari 9-0.

Pada kondisi 3, dimana diberi kondisi switch B0 menjadi 1, B2 menjadi 0 serta B3 diberi clock. maka, output yang terjadi yaitu seven segment manyala dan menampilkan angka 0.

Pada kondisi 4, dimana diberi kondisi switch B0 menjadi 1, B2 menjadi 1 serta B3 diberi clock. maka, output yang terjadi yaitu seven segment menyala dan menampilkan angka 0.

2] Analisa pengaruh IC counter pada rangkaian !

Untuk IC Counter yang digunakan yaitu IC 74192 yang mana dapat mencounter atau mencacah biner dacade atau dari 0000 sampai 1001 dalam biner atau 0 hingga 9 dalam desimal dan pada rangakaian di percobaan 3 merupakan jenis counter down sehingga menghitung mundur dari 9 hingga 0.

3] Analisa fungsi 2 gerbang OR pada rangkaian !

Gerbang OR berpengaruh terhadap rangkaian dimana OR 1 menuju ke kaki IC Counter pada kaki input UP dan untuk OR 2 dimana dari output IC Counter menuju kembali ke kaki gerbang OR 1 dan pada rangakaian mengalami counter down karena pada OR 1 menuju pin DN yang diberi clock dan pin UP diberi logika 1 dan juga untuk kedua gerbang OR inilah akan menentukan Counter Up dan Down dari rangkaian.

.jpeg)

Tidak ada komentar:

Posting Komentar